Parallel Computing (2)

Parallel Computing (2)

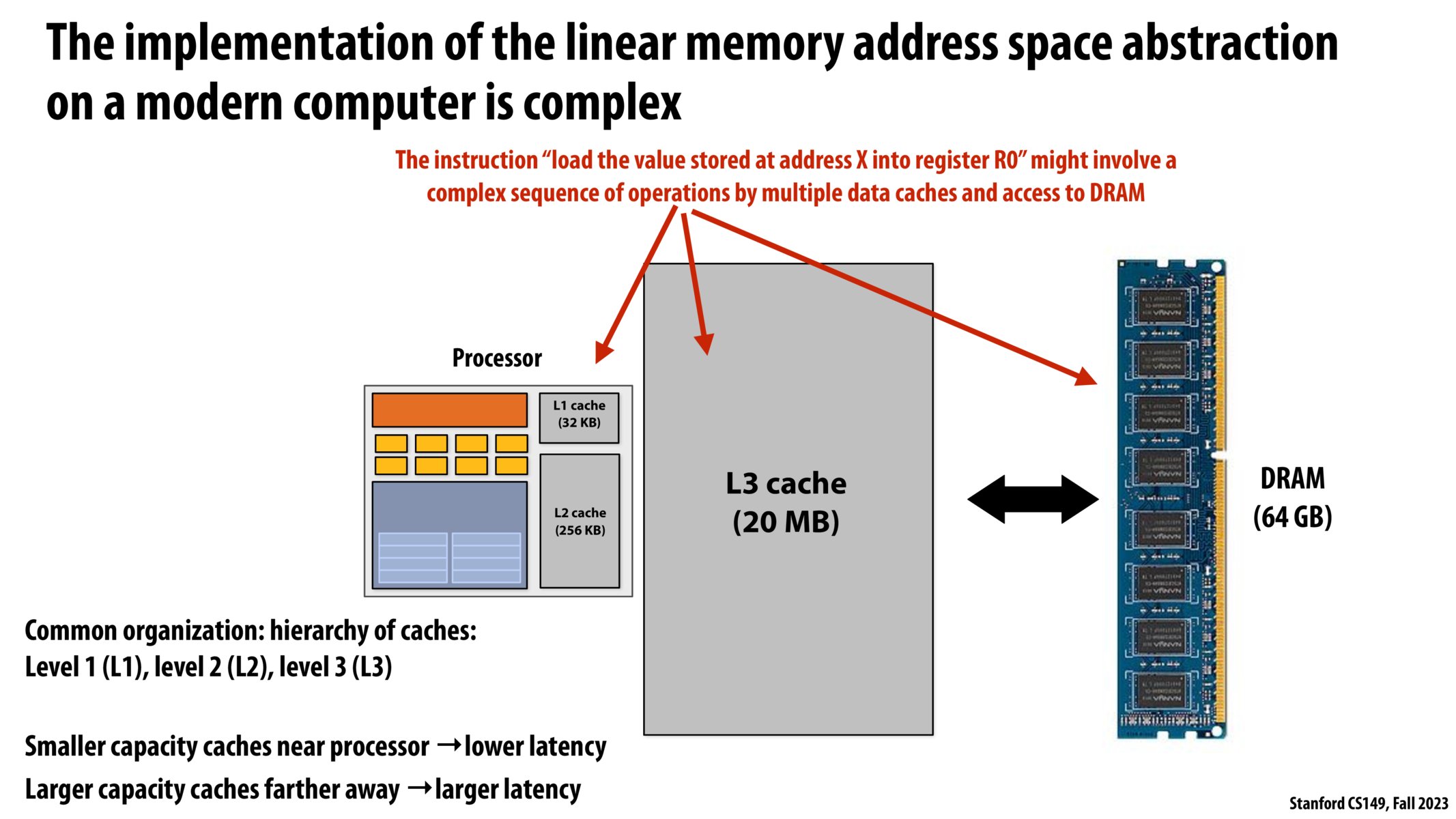

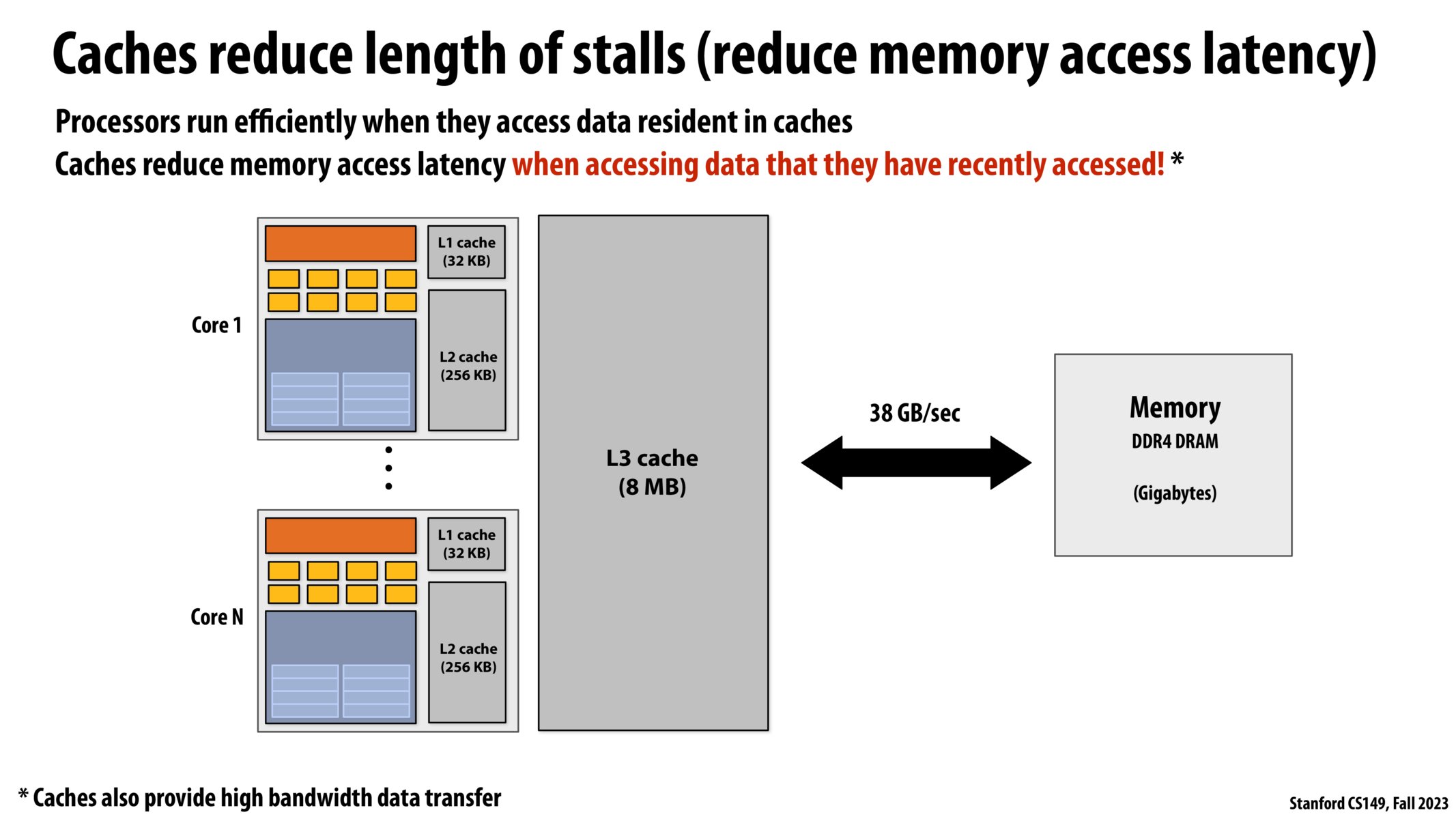

Holi对多级缓存的认识

多种miss:

- cold miss

- conflict miss

- capacity miss

多种并行思路

在本次课程中,除开上一次课程介绍的超标量(指令级别并行),又介绍了多种并行处理器思路来提升吞吐量(throughput),考虑到

- 并行执行

- 访问存储器的延迟(latency)

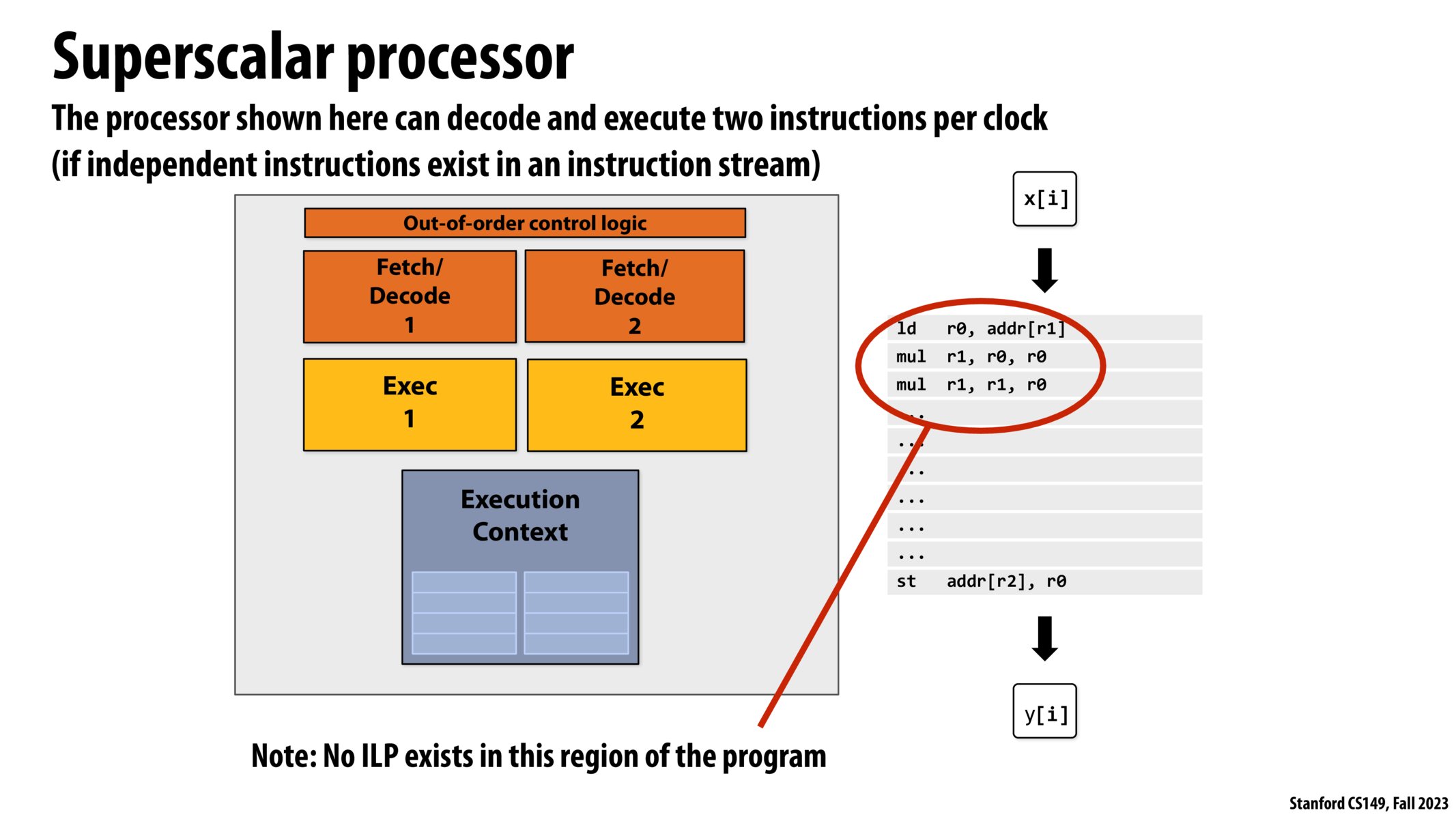

超标量(super scalar)

对于同一个程序,可以同时抓取预先编译好的多个可并行指令进行执行。

程序中的并行是由硬件自动发现的。

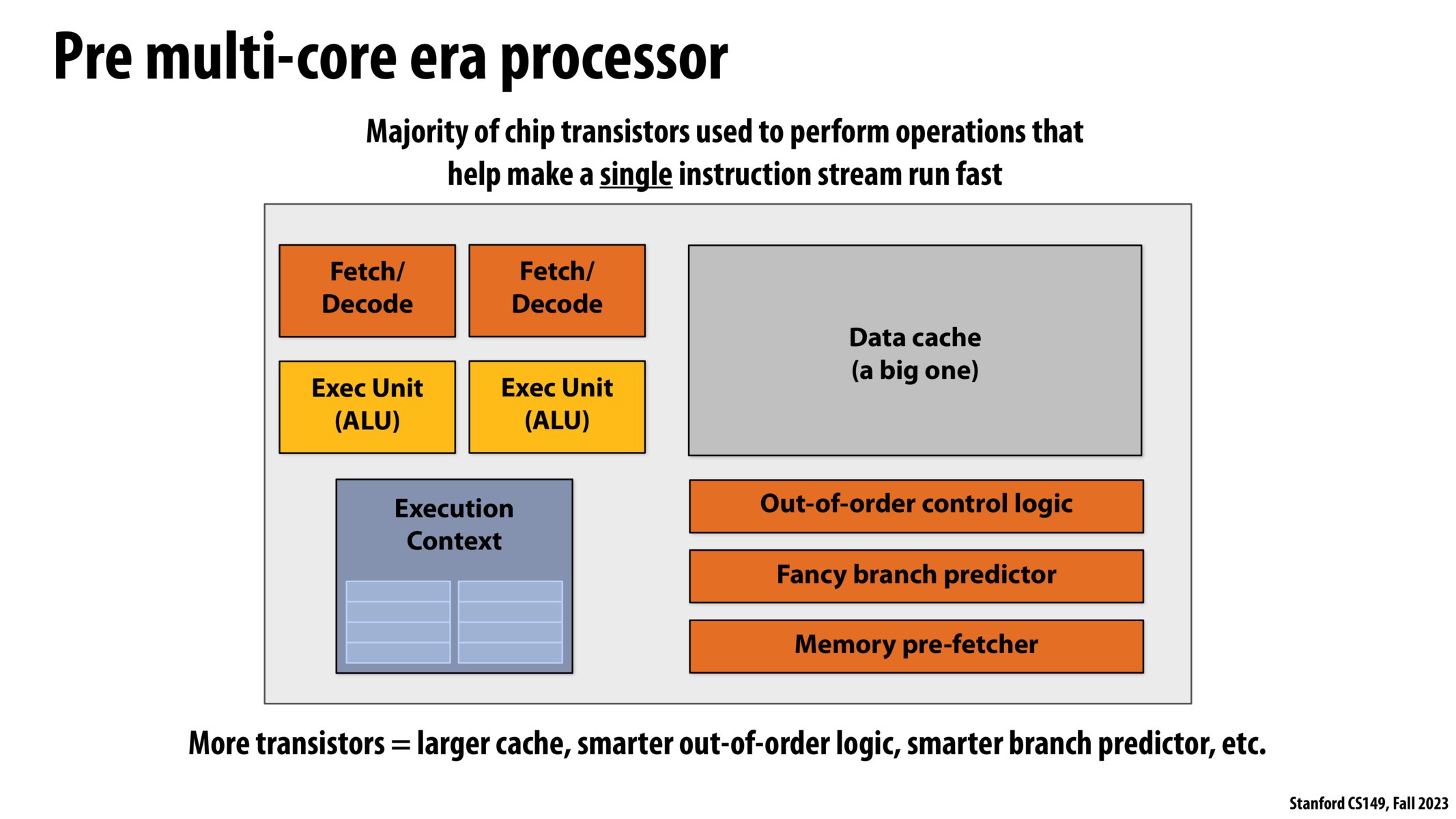

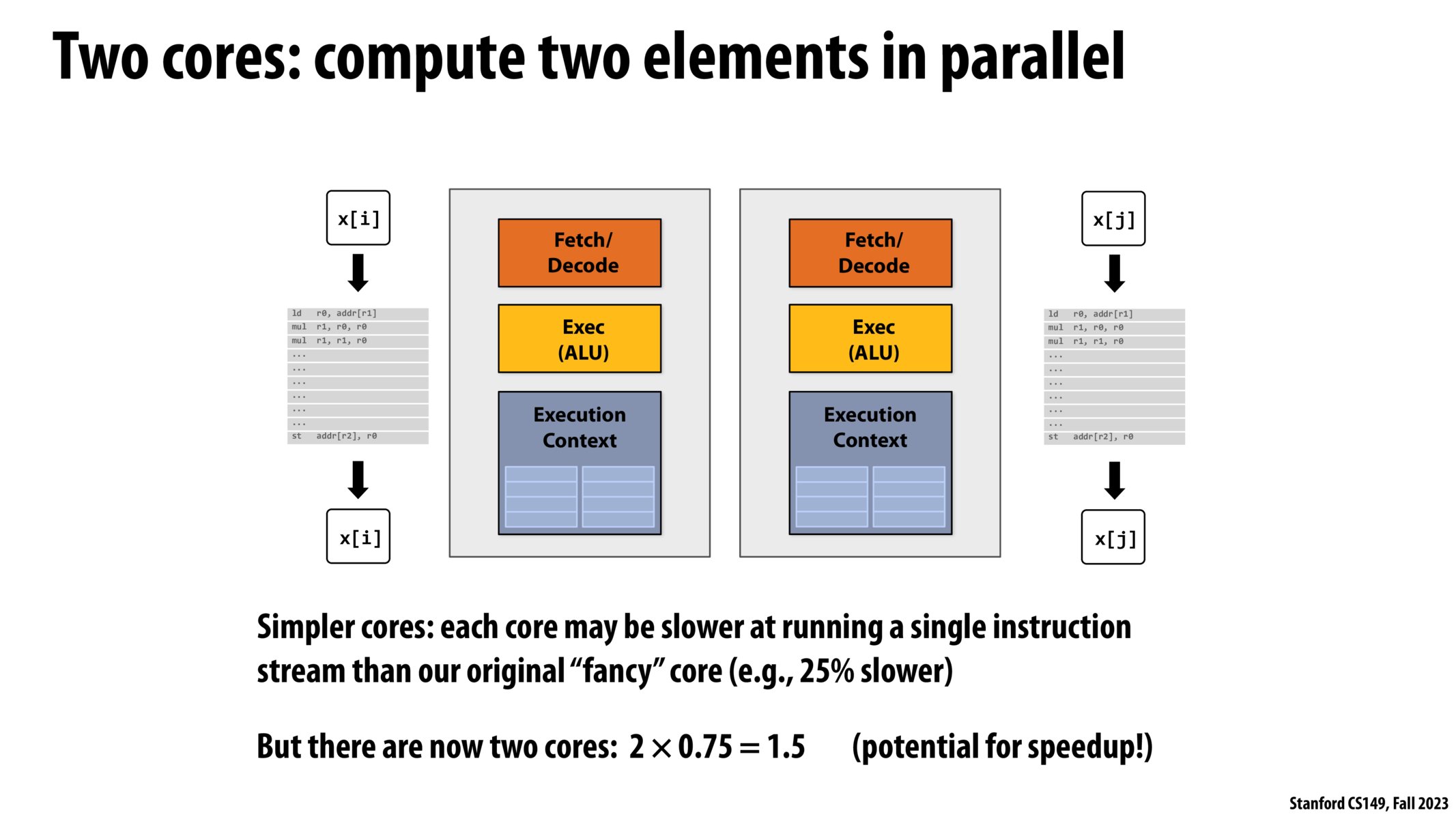

多核处理器

在还没出现多核处理器的时候,人们设计CPU往往致力于增加更多的模块来让单条指令执行地更快。

但是通过删去这些额外的模块,实际上可以实现多个核的处理器(单核的性能比原来要差)。

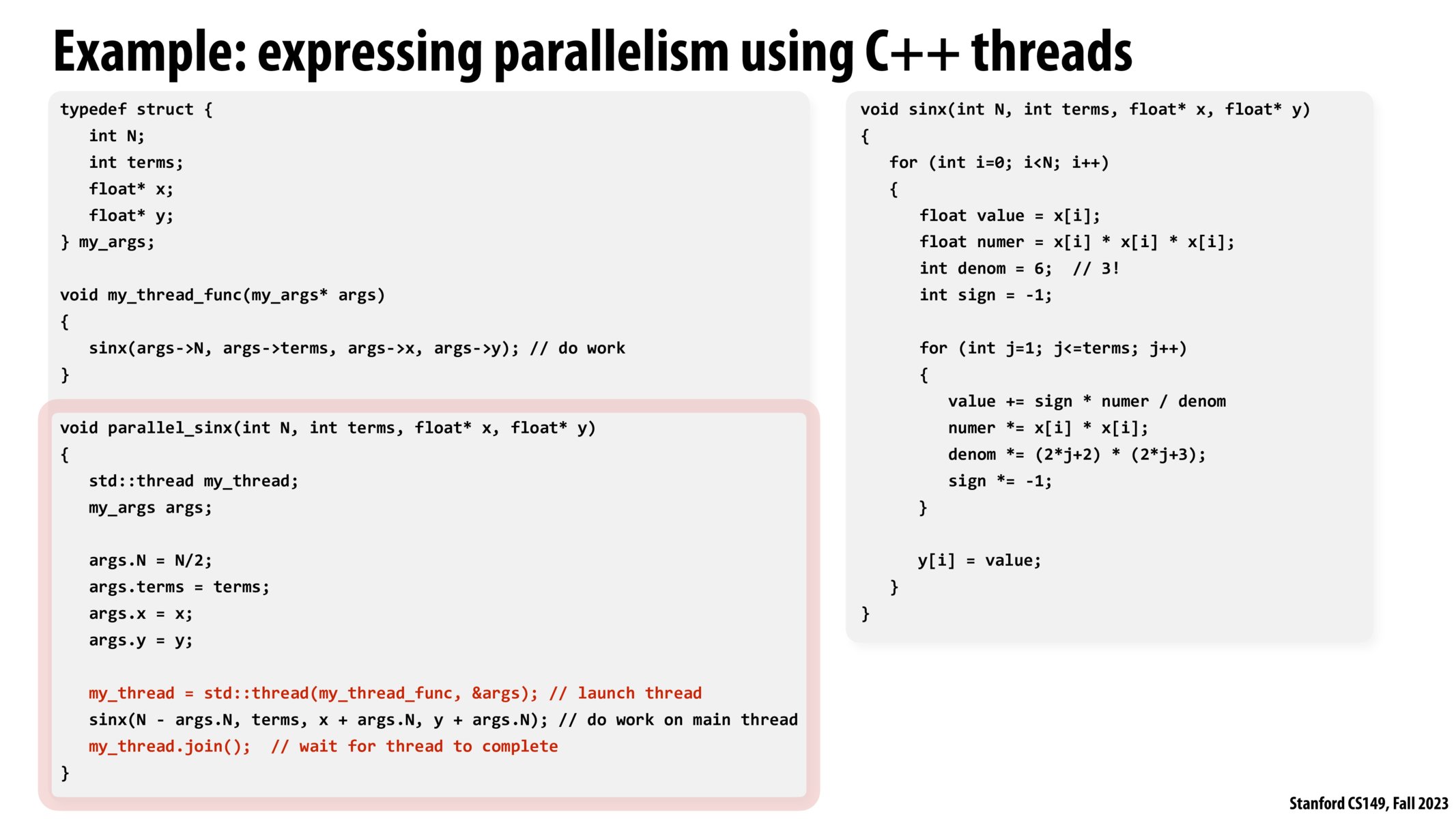

这样通过在程序中定义多个线程,就可以比较充分地利用两个核的性能。程序示意图如下所示:

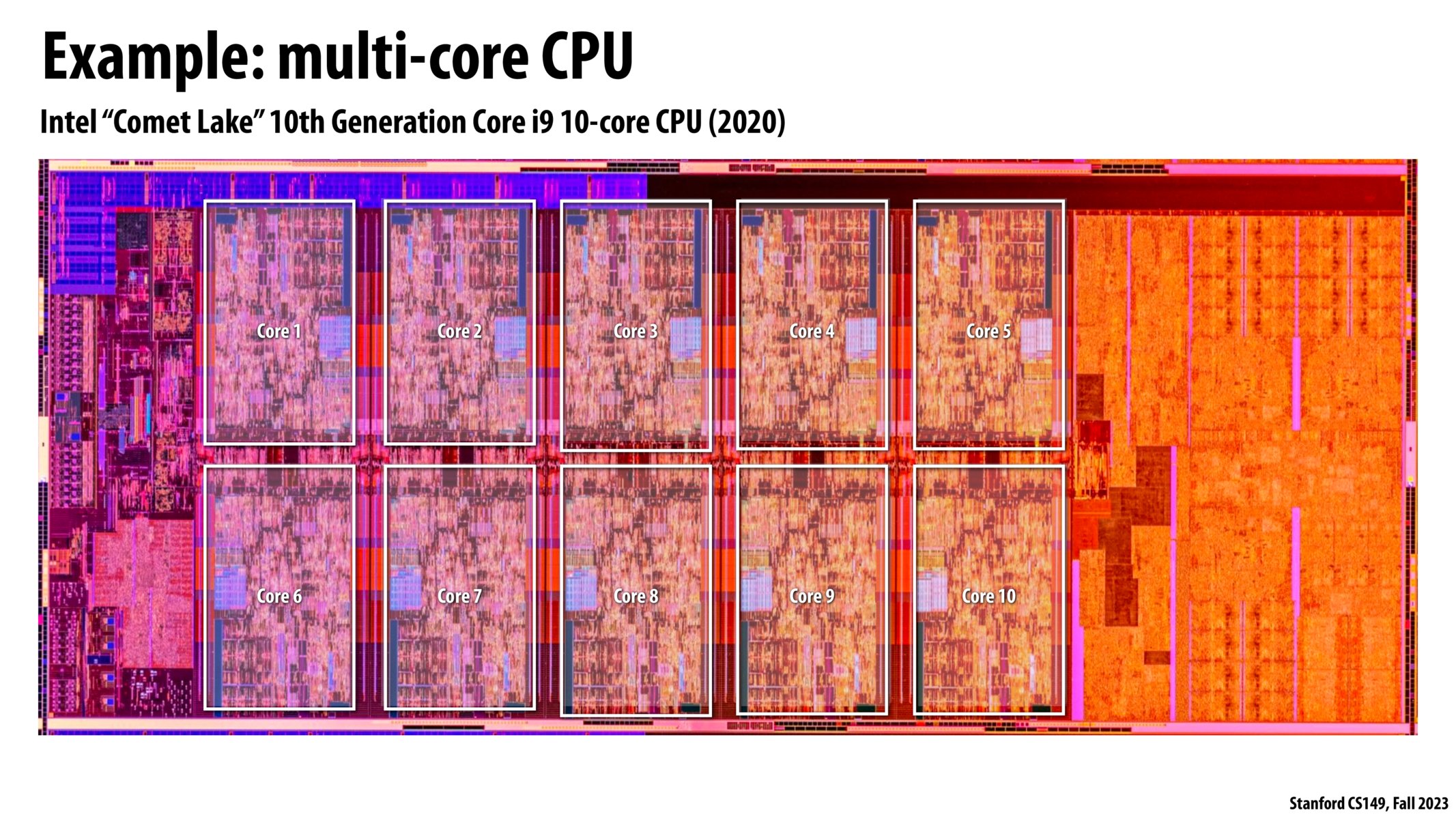

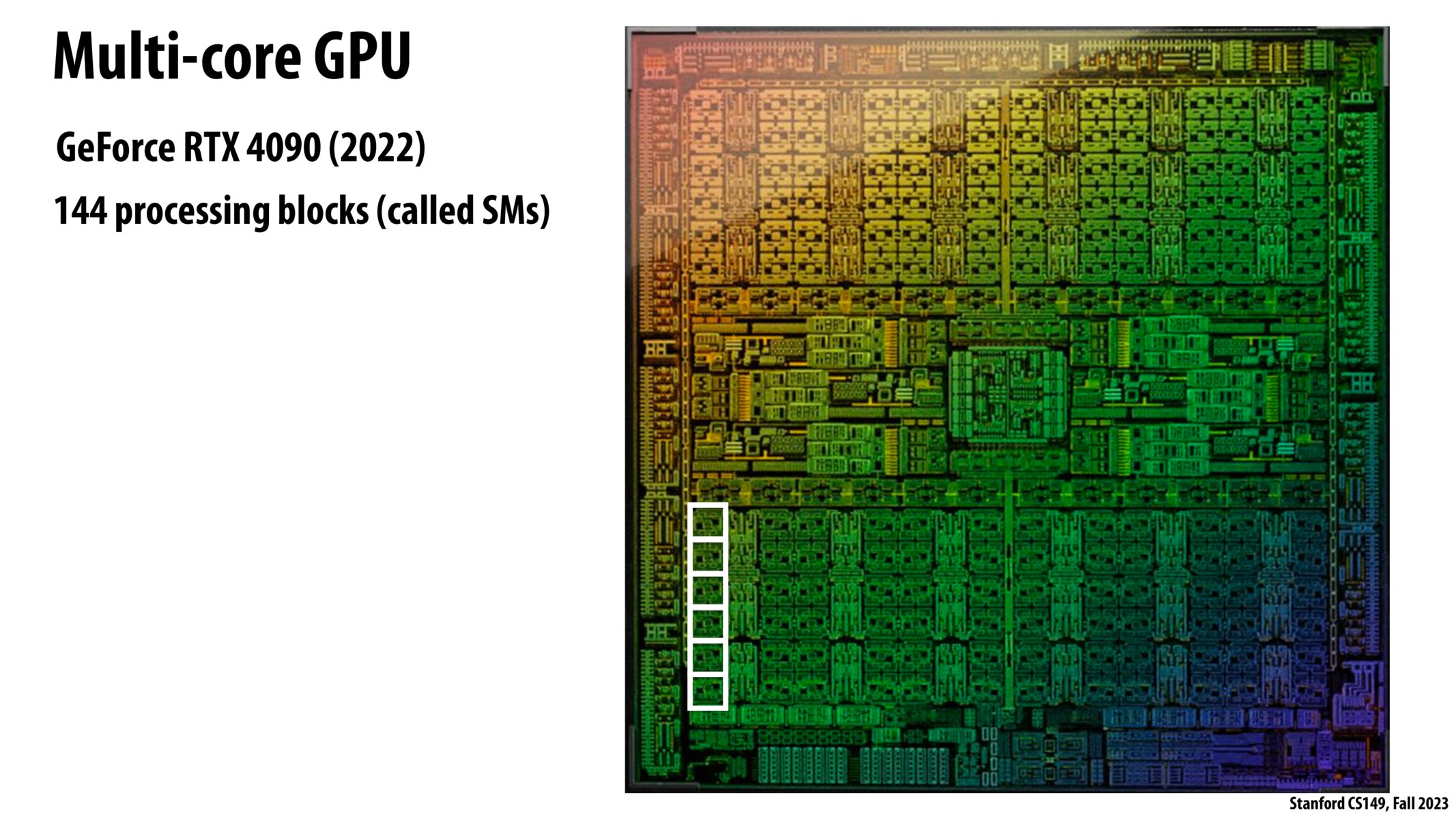

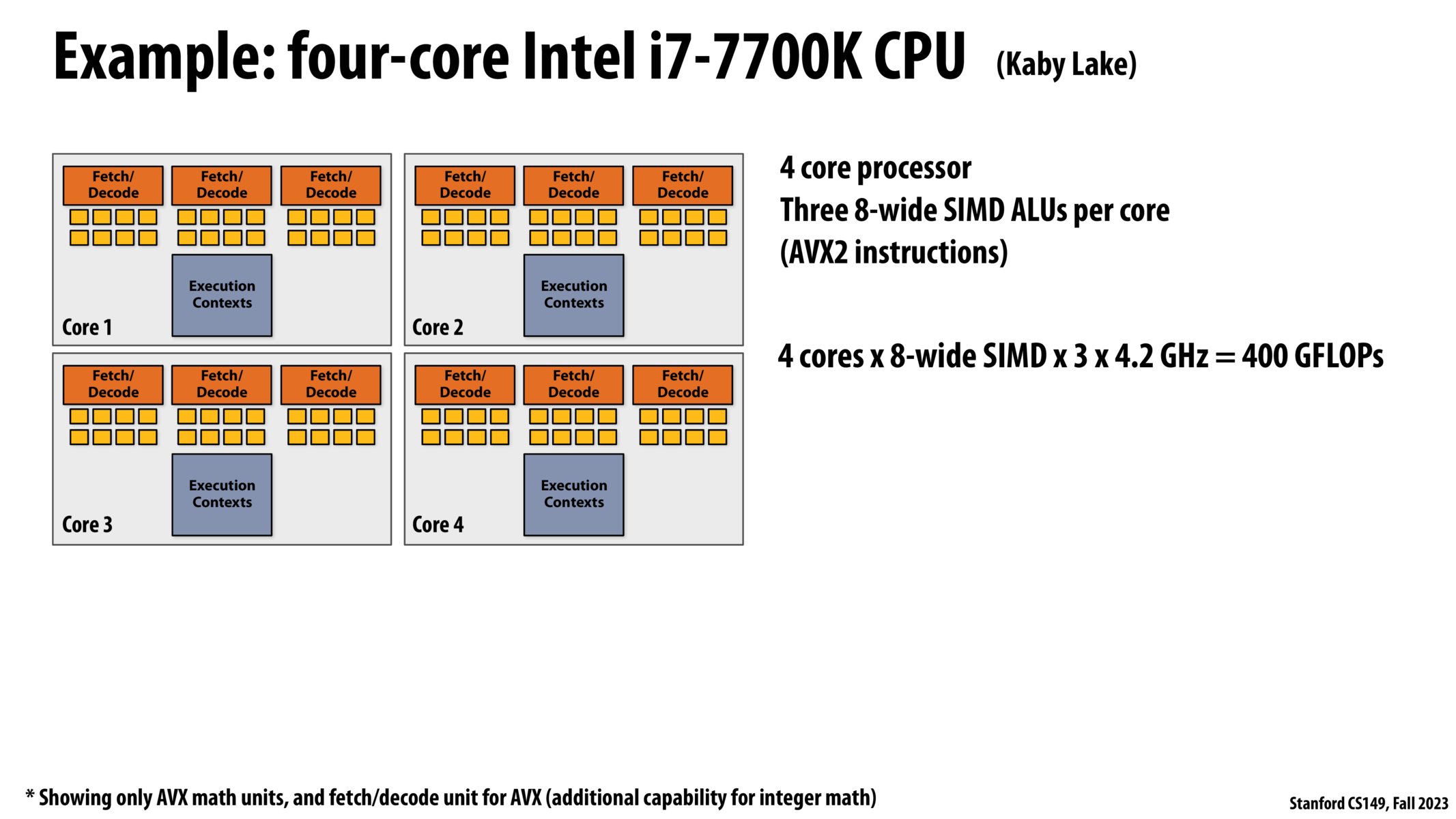

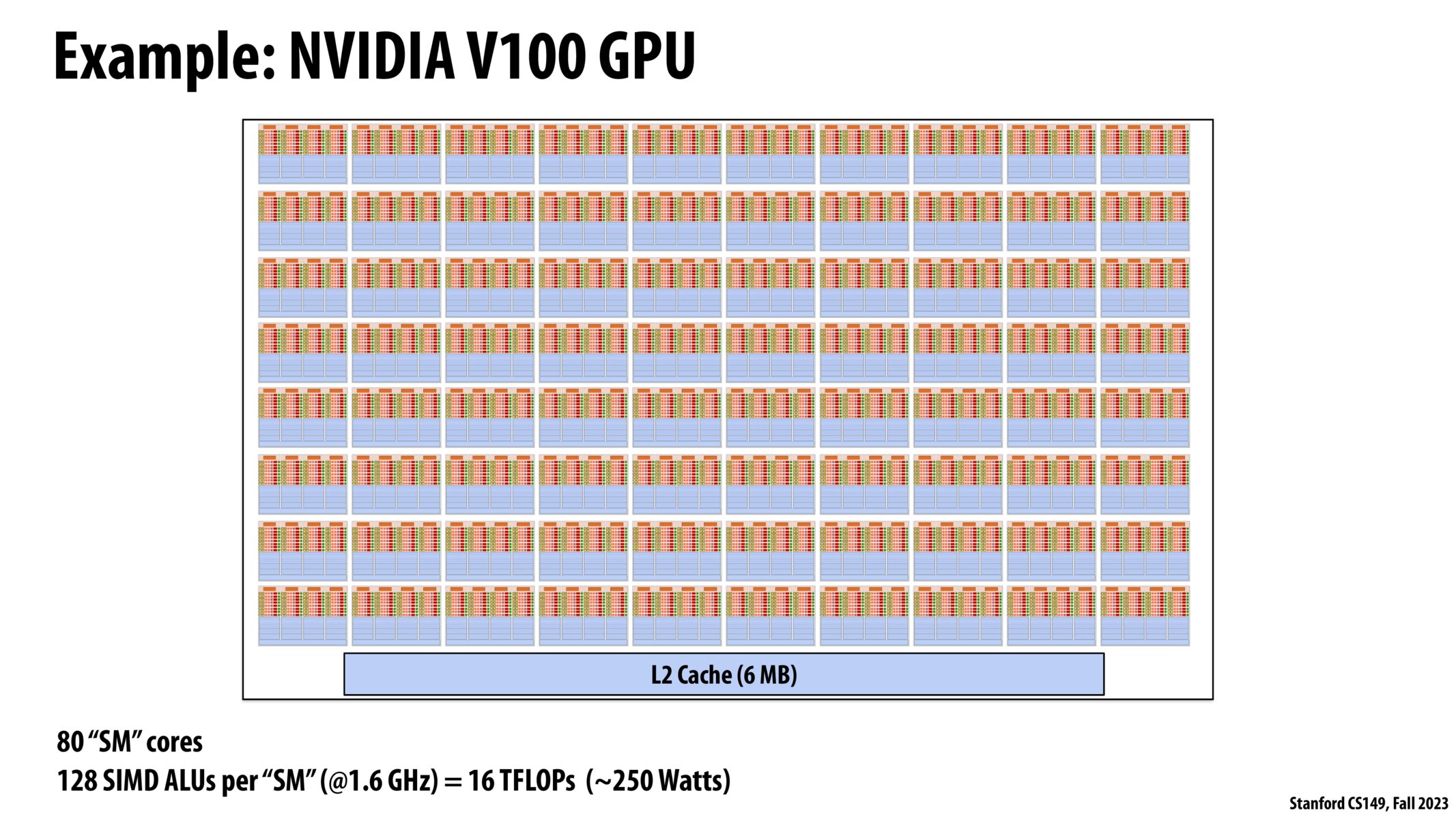

现代多核处理器的例子:

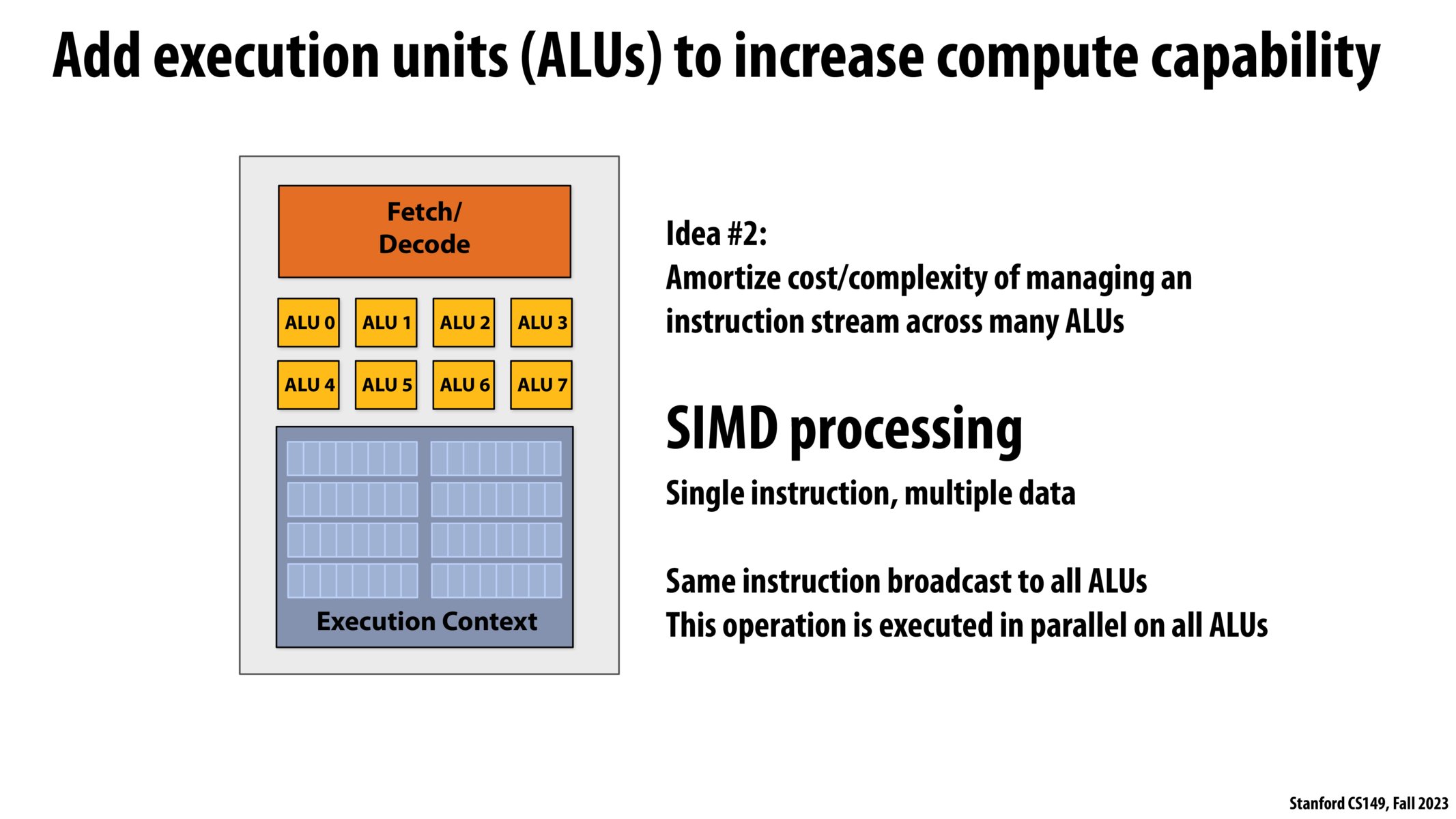

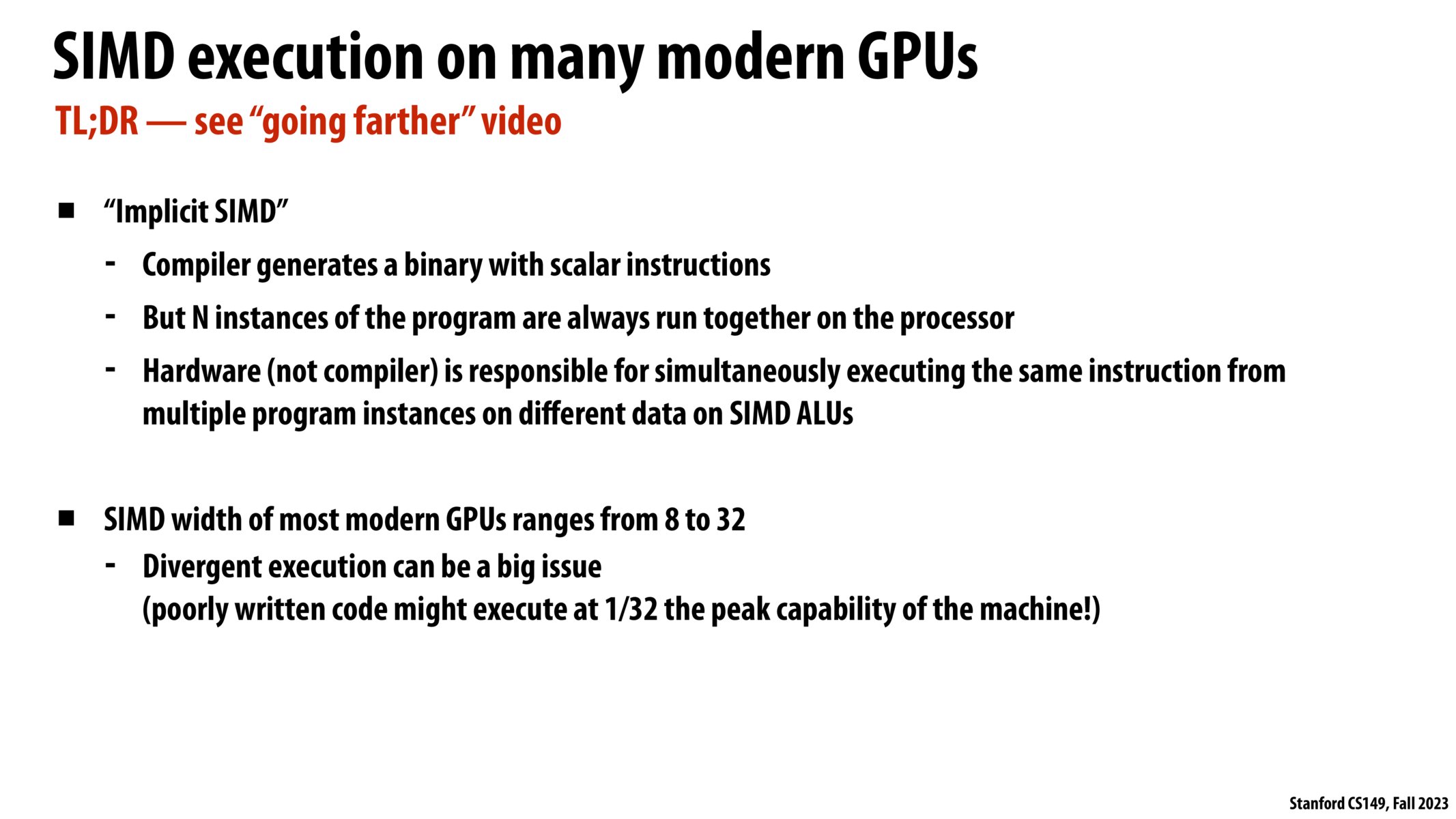

单指令多数据流(SIMD)

single instruction, multiple data。

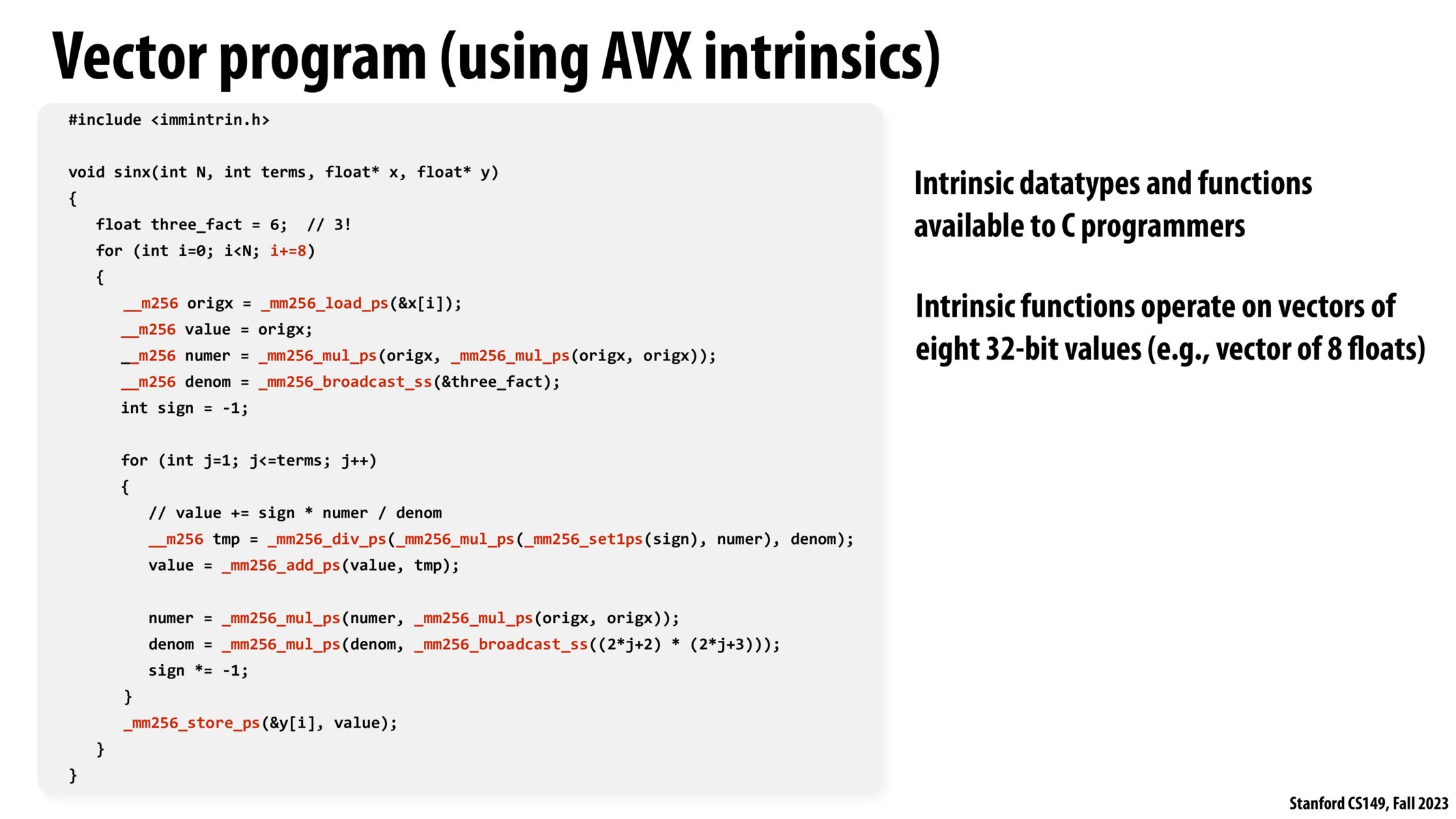

通过引入更多的ALU(计算单元),使得可以在同一时间对多个数据进行相同的运算操作。

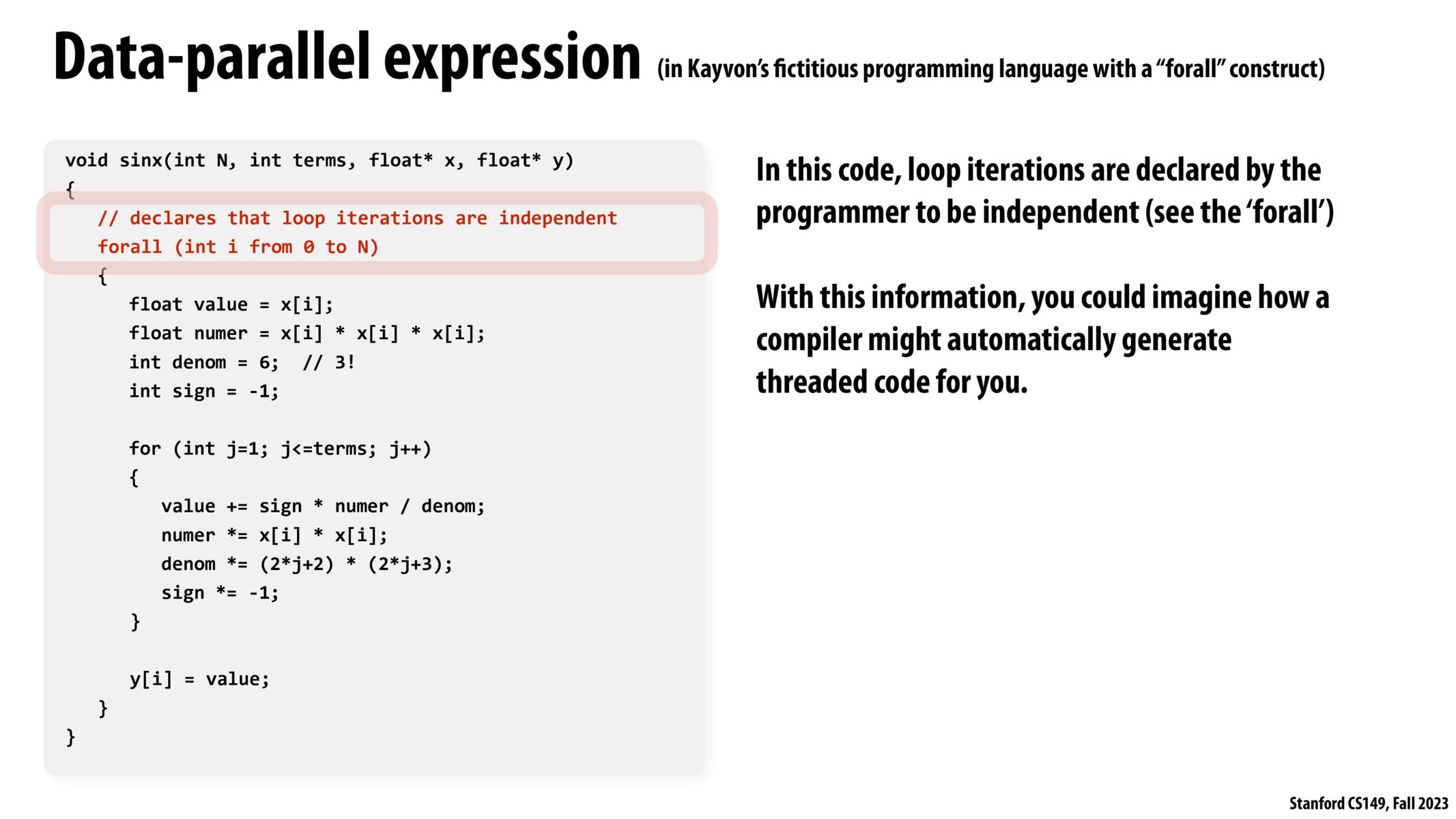

如上架构可以执行如下的数据并行程序:

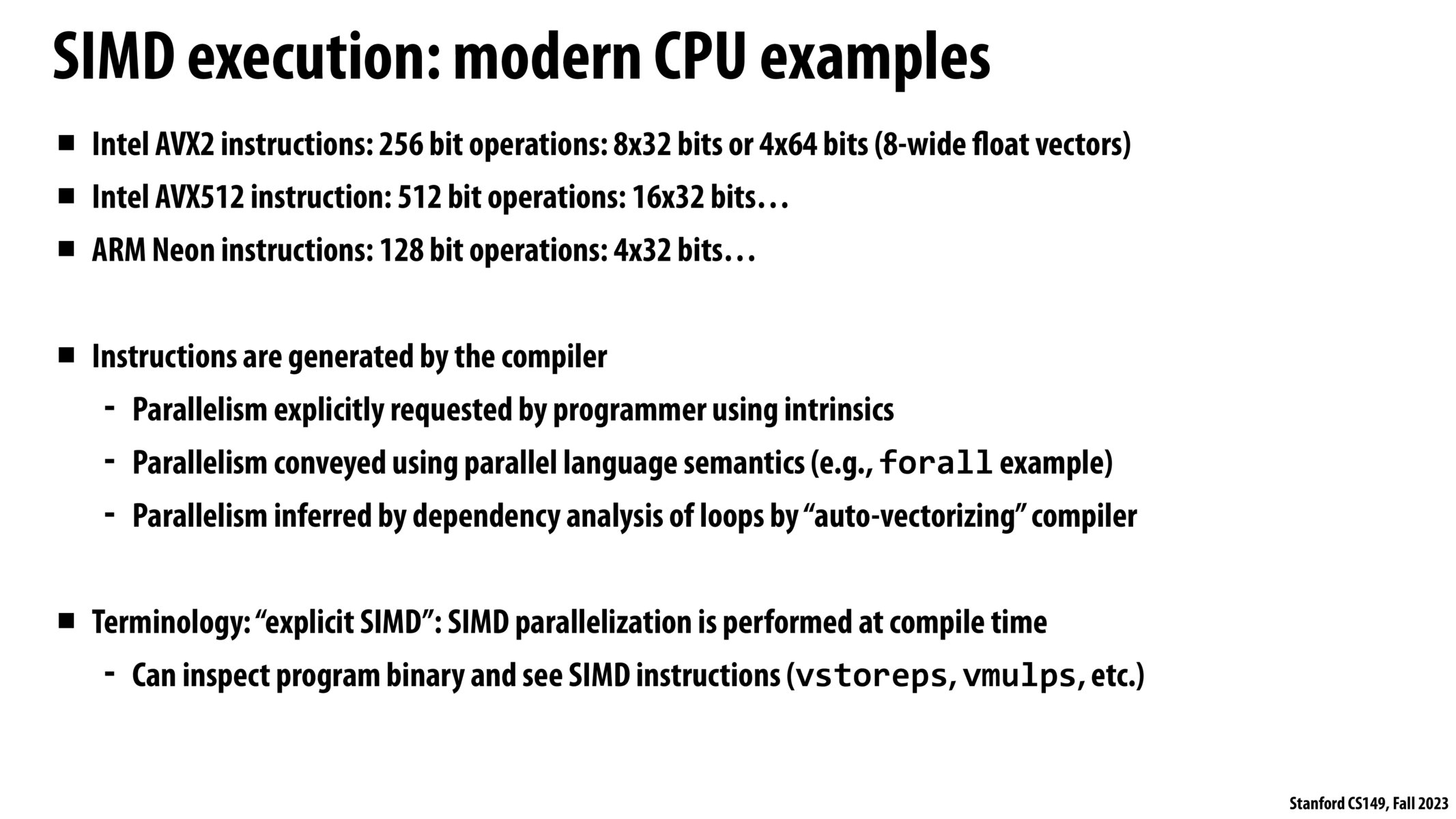

【注意上述第二个程序既可以被多核处理器处理也可以被SIMD处理】向量化是由编译器实现(explicit)或者在runtime时由硬件实现(implicit)。

一些行话

- 指令流一致性、相干性(coherence)

- 相同指令可以同时作用于多个数据

- 一致执行对于SIMD来说是必要的

- 一致执行对于多核并行并不是必要的

- 差异执行(divergent)

- 指令流缺乏一致性

例子

访问存储的加速

数据预加载

目前有一些现代CPU架构,其可以在使用到数据前自动地进行分析,并提前加载数据,从而减少stall,但是错误估计实际上会降低性能。

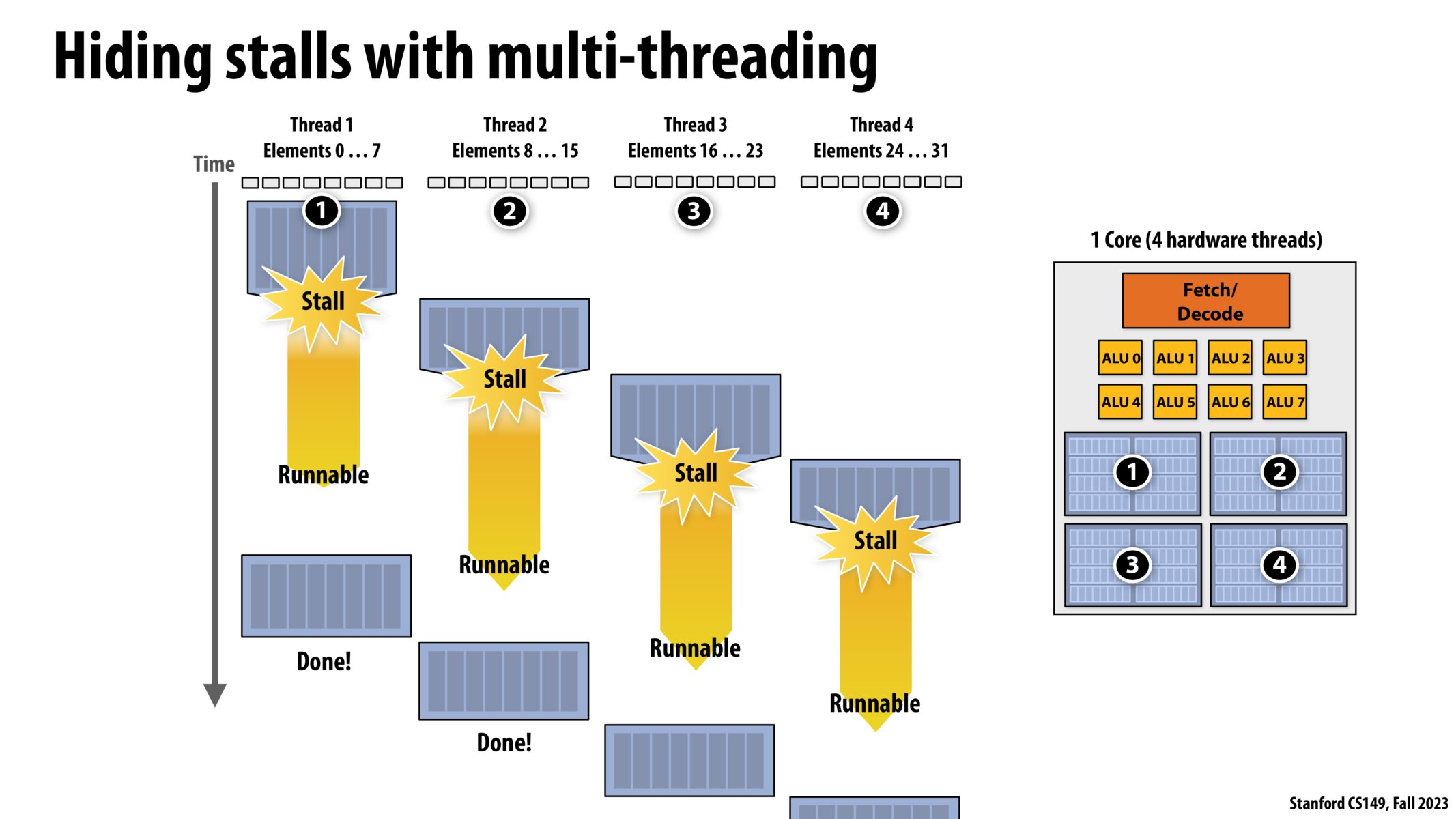

多线程减少stall

在同一个核上interleave(交织)多个线程来提升利用率。

执行单个线程的时间实际上可能仍然很长,但是多个线程总体执行时间相较于串行执行变少了。

评论

匿名评论隐私政策